英伟达台积电密谋的“新核弹”,计算光刻如何改变2nm芯片制造?

导读:黄仁勋、New Bing解读计算光刻:如何影响芯片制造未来?

作者 | ZeR0

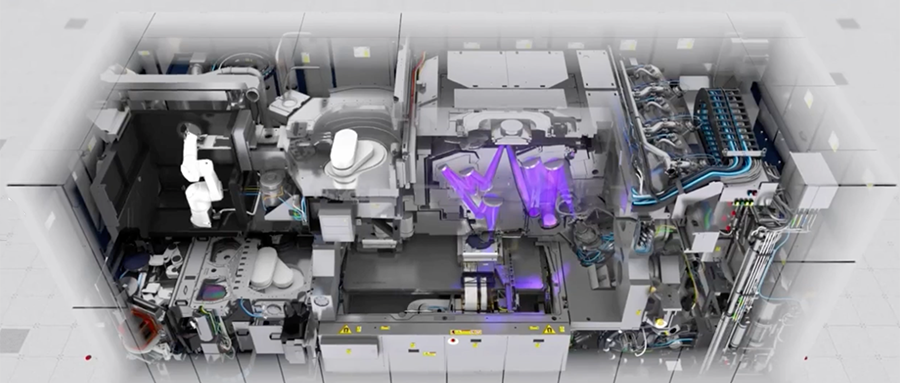

芯东西3月23日报道,在英伟达GTC大会上,英伟达创始人兼CEO黄仁勋宣布了一项突破性的cuLitho计算光刻技术软件库,它将计算光刻加速40倍以上,为2nm及更先进的工艺奠定基础。

光刻机的重要性,在芯片行业里已经如雷贯耳。它是半导体工业皇冠上的明珠,是芯片制造过程中最复杂、最昂贵、最关键的环节,其成本约占整个硅片加工成本的1/3甚至更多。而计算光刻是芯片设计和制造领域中最大的计算工作负载,其速度提高对于挺进先进制程节点至关重要。

cuLitho是英伟达与全球最大晶圆代工厂台积电、全球最大光刻机巨头阿斯麦、全球最大EDA巨头新思科技密切合作,秘密研发近四年的“核弹”。

使用cuLitho的晶圆厂,每天可生产3-5倍多的光掩膜,仅使用当前配置电力的1/9。台积电和新思科技正将cuLitho整合到最新一代英伟达Hopper架构GPU的软件、制造工艺和系统中,阿斯麦计划在让所有计算光刻软件产品支持GPU,台积电将于6月开始对cuLitho进行生产资格认证。

那么,计算光刻技术到底起到什么作用?它究竟对于光刻机以及先进芯片制造产生多重要的影响?为什么英伟达推出加速计算光刻的新技术,会得到三大半导体巨头的盛赞和追捧?

结合黄仁勋“光刻机小课堂”和微软New Bing聊天机器人回复的解释,我们将这些问题一一解答。

01.

黄仁勋光刻机小课堂生动开讲

EUV光刻系统价值超过2.5亿美元

根据复旦大学微电子学院在去年5月发表的《先进光刻技术的发展历程与最新进展》综述文章,光刻技术不断提高的分辨率与图形复制精度成功地将集成电路制造线宽从40多年前的2~3μm缩小到先进的10~15nm。当逻辑技术节点到达5nm,后段必须引入EUV工艺,以减小掩模版数目、节省成本,并提高套刻精度和可靠性。

中国台积电、韩国三星、美国格罗方德、英特尔等先进的芯片代工厂及IDM大厂在引入EUV技术方面已有技术积累。但中国大陆暂时没有EUV光刻机,芯片代工厂都是用193nm水浸没式光刻机多次曝光实现7nm逻辑芯片的光刻工艺流程。

在英伟达GTC大会上,为了让大家理解加速计算光刻的重要性,黄仁勋特意给全球观众上了一堂“光刻机小课堂”。

他讲解道,光刻是在晶圆上创建图案的过程,是芯片制造过程的起始阶段,包括两个阶段——光掩膜制造和图案投影。从根本而言,这是一个物理极限下的成像问题,光掩膜如同芯片中的模板光线被阻挡或穿过光掩膜到达晶片以形成图案。

光线由阿斯麦极紫外(EUV)光刻系统产生,每个系统的价值超过2.5亿美元。

阿斯麦EUV采用了一种颠覆性的方式来制造光线,激光脉冲每秒向一滴锡发射5万次,使其汽化,产生一种能发射13.5nm EUV光的等离子体,几乎是X射线。

随后,多层镜面引导光线至光掩膜。光掩膜版中的多层反射器利用13.5nm光的干涉图案,实现更精细特征,精细度可达到3nm。晶圆的定位精度达到1/4nm,并且每秒对准2万次以消除任何振动的影响。

光刻之前的步骤同样令人不可思议。

黄仁勋解释说,计算光刻模拟了光通过光学元件并与光刻胶相互作用时的行为(这些行为是根据麦克斯韦方程描述的),应用逆物理算法来预测掩膜版上的图案,以便在晶圆上生成最终图案。掩膜上的图案与最终特征完全不相似。

据黄仁勋介绍,英伟达H100 GPU需要89块掩膜版,以前在CPU上运行时,处理单个掩膜版需要两周时间,而在GPU上运行cuLitho只需8小时。

此外,台积电可通过在500个DGX H100系统上使用cuLitho加速,将功率从35MW降至5MW,替代此前用于计算光刻的40000台CPU服务器。

02.

计算光刻技术有多重要?

提高光刻机分辨率,影响芯片性能和质量

我们让New Bing用简单通俗的话解释计算光刻技术的重要性。

它回复说,芯片制造就是在晶圆上刻画出很多很多的晶体管和互连线路,形成电路和功能。随着芯片的功能越来越强大,晶体管和互连线路要越来越小,这样才能放得下更多的元件。

光刻机是芯片制造过程中最核心的设备,其性能和精度决定了芯片能实现多小的特征尺寸和多高的集成度,也就影响了芯片的速度、功耗、容量等指标。

它像一台高精度的相机,负责把芯片设计的图案转移到晶圆上,形成芯片的基本结构。但随着芯片的结构越来越小,光刻机所用的光线就不够细致,会产生一些模糊和失真的现象,影响芯片的性能和质量。

而计算光刻技术通过软件来模拟和优化光刻过程中的各种元素,比如光源、掩膜版、镜头等,让光线能够更精确地照射到晶圆上,帮助光刻机更好地刻画出芯片的微小结构,实现更高的分辨率和效率,避免一些错误和缺陷。

总而言之,这项技术可以帮助光刻机实现更高的分辨率和效率,提高芯片的性能和质量,帮助芯片制造实现更小的特征尺寸和更高的集成度,制造出更先进和更复杂的芯片。

03.

四大好处、四项技能

助攻晶圆厂挺进2nm节点

据New Bing整理,计算光刻技术有四大好处:

(1)提高光刻分辨率,实现更小的特征尺寸和更高的集成度。

(2)减少衍射像差和其他光学误差,提高成像质量和工艺窗口。

(3)缩短掩膜版的制作时间,降低功耗和成本,提高生产效率。

(4)支撑2nm及更先进的制程工艺,为新型解决方案和创新技术奠定基础。

具体来说,计算光刻技术主要具备四项技能:

(1)通过数值模拟来预测和评估不同波长、不同掩模、不同曝光条件下的成像效果,为工艺设计提供指导和参考。

(2)通过源掩模协同优化(SMO)来调整曝光源形状和掩模图形以改善成像质量和过程窗口。

(3)通过多重曝光(Multiple Patterning)来将复杂图形分解为多个简单图形,并分别进行曝光和叠加以实现更小特征尺寸。

(4)通过深度学习等人工智能方法来提高计算效率和精度,并实现自动化优化。

04.

结语:加速计算光刻

将芯片制造大幅降本增效

看完全文后,是不是对于加速计算光刻的重要性有了更深的理解?

黄仁勋说,计算光刻每年消耗数百亿CPU小时。大型数据中心24 x 7全天候运行,以便创建用于光刻系统的掩膜版。这些数据中心是芯片制造商每年投资近2000亿美元的资本支出的一部分。

这也是为什么英伟达新推出的cuLitho会得到台积电、阿斯麦、新思科技的大力支持。

随着光刻技术临近物理极限,这项技术通过加速计算光刻流程,将有助于晶圆厂缩短原型周期时间、提高产量、减少碳排放,为2nm及更先进的工艺奠定基础,并使得曲线掩模、high NA EUV、亚原子级光刻胶模型等新技术节点所需的新型解决方案和创新技术成为可能。